#### МИНОБРНАУКИ РОССИИ

Федеральное государственное бюджетное образовательное учреждение высшего профессионального образования

«Ухтинский государственный технический университет» (УГТУ)

# КОМПЬЮТЕРНАЯ И МИКРОПРОЦЕССОРНАЯ ТЕХНИКА В ИССЛЕДОВАНИИ И УПРАВЛЕНИИ ЭЛЕКТРОПРИВОДА

Курсовая работа

Методические указания

УДК 621.316.5(075.8) ББК 31.264 я 7 К 68

#### Коротков, Ю. В.

К 68 Компьютерная и микропроцессорная техника в исследовании и управлении электропривода. Курсовая работа [Текст] : метод. указания / Коротков Ю. В., Тетеревлёва Е. В. – Ухта : УГТУ, 2015. – 38 с.

Методические указания предназначены для руководства при выполнении курсовой работы по дисциплине «Компьютерная и микропроцессорная техника в исследовании и управлении электропривода» бакалаврами и магистрами по направлению подготовки 140400 Электроэнергетика и электротехника.

УДК 621.316.5 (075.8) ББК 31.264 я7

Методические указания рассмотрены и одобрены заседанием кафедры ЭАТП от 28.04.2015, пр. №4.

Рецензент: А. Э. Старцев, доцент кафедры ЭАТП Ухтинского государственного технического университета.

Редактор: Полетаев С. В., ст. преподаватель кафедры ЭАТП Ухтинского государственного технического университета.

Корректор и технический редактор: А. Ю. Васина.

В методических указаниях учтены предложения рецензента и редактора.

План 2015 г., позиция 113.

Подписано в печать 30.06.2015. Компьютерный набор.

Объём 38 с. Тираж 100 экз. Заказ №297.

© Ухтинский государственный технический университет, 2015 169300, Республика Коми, г. Ухта, ул. Первомайская, д. 13. Типография УГТУ.

169300, Республика Коми, г. Ухта, ул. Октябрьская, д. 13.

#### ОБЩИЕ ПОЛОЖЕНИЯ

Дисциплина «Компьютерная и микропроцессорная техника в исследовании и управлении электропривода» принадлежит к числу специальных дисциплин для студентов направления 140400.

Дисциплина нацелена на формирование профессиональных компетенций ПК-10, 11,12, 14 обучающегося.

Студент должен обладать следующими профессиональными компетенциями (ПК):

- общепрофессиональными:

- способностью формулировать технические задания, разрабатывать и использовать средства автоматизации при проектировании и технологической подготовке производства (ПК-10);

- готовностью применять методы анализа вариантов, разработки и поиска компромиссных решений (ПК-11);

- готовностью применять основы инженерного проектирования технических объектов (ПК-12);

- готовностью использовать прикладное программное обеспечение для расчета параметров и выбора устройств электротехнического и электроэнергетического оборудования (ПК-14).

Дисциплина предусматривает следующие формы организации учебного процесса: самостоятельная работа, лабораторные работы, курсовая работа, зачёт, экзамен.

#### **ВВЕДЕНИЕ**

Широкое внедрение микропроцессорной техники во все сферы человеческой деятельности, эффективность этого процесса неразрывно связаны как развитием многочисленных сложных технических разработок, так и с уровнем подготовки в этой области специалистов самого разного профиля. Соответствие функциональных возможностей микропроцессорных систем и технологического назначения, связанных с ними объектов обуславливает необходимость соответствующей подготовки специалистов.

Современные специалисты в области электронной техники и те, кто только еще изучает, должны обладать знаниями в области микропроцессоров и микропроцессорных систем, т. е. сведениями как об её аппаратной, так и о про-

граммной частях. Микропроцессоры являются основой совершенно нового поколения интеллектуальных машин.

Наиболее важными и ответственными элементами современных систем автоматики являются управляющие микро-ЭВМ. Именно они обеспечивают высокую надёжность, точность и качество управления, возможность построения как иерархических, так и распределённых структур управления, быструю и качественную обработку поступающей извне информации, многообразие режимов работы, возможность самоконтроля и самодиагностики, резервирования, дружественный интерфейс с пользователями.

Важным достоинством микро-ЭВМ является её универсальность. Одна и та же микро-ЭВМ может сопрягаться с самыми разнообразными внешними устройствами, датчиками и объектами управления. При этом изменение выполняемых микро-ЭВМ функций производится простой заменой или коррекцией управляющей программы.

Разработка и наладка систем автоматики на основе микро-ЭВМ имеет существенную специфику, связанную с тем, что правильное и результативное функционирование таких систем обеспечивается комплексом взаимодействующих аппаратных и программных средств.

Аппаратные средства (hard) служат как для построения микро-ЭВМ, так и для её связи с другими устройствами. Часто в качестве аппаратных средств используют БИС, составляющие микропроцессорные комплекты микросхем. Программные средства (soft), в конечном итоге, обеспечивают нужный режим работы всей системы автоматики. К области программных средств относятся: системы команд конкретных микро-ЭВМ, системные и прикладные программы, методы и принципы составления программ, инструментальная поддержка программирования.

Следует отметить взаимосвязь и взаимообусловленность программных и аппаратных средств, в решении конкретной задачи управления. При этом усложнение аппаратных средств часто даёт возможность упростить программные средства и, наоборот, упрощение аппаратных средств может вести к усложнению программных. Рациональное разделение функций между программными и аппаратными средствами — одна из самых важных задач, решаемых при создании систем автоматики.

Разработанные методические указания предназначены для выполнения курсовой работы.

# ПОСЛЕДОВАТЕЛЬНОСТЬ ПРОЕКТИРОВАНИЯ КУРСОВОЙ РАБОТЫ

Цель курсового проектирования — закрепление студентами полученных знаний по курсу «Компьютерная и микропроцессорная техника в исследовании и управлении электропривода» и приобретение навыка в разработке систем и средств автоматизации на базе современных достижений микропроцессорной техники.

Примерная тема курсовой работы:

Автоматизация технологического процесса (название технологического процесса) на основе микропроцессорной элементарной базы. Название технологического процесса задается преподавателем.

Примерное содержание курсовой работы выглядит следующим образом:

- 1. Введение.

- 2. Анализ технологического процесса и обоснования необходимости автоматизации с использованием достижений современной микропроцессорной элементарной базы. Составляется структурная схема предложенной системы.

- 3. На основании предложенной структурной схемы выбираются из справочника конкретные элементы и составляется общая принципиальная схема.

- 4. Составляется алгоритм работы предложенной системы.

- 5. Разработка программы в среде для программирования контроллеров CoDeSys по составленному алгоритму.

- 6. Проводится расчёт основных узлов канала сбора аналоговых данных микропроцессорной системой.

- 7. Проводится расчёт надёжности предложенной системы.

- 8. Заключение.

- 9. Используемая литература.

- 10. Приложение (листинг программы).

- 11. Графическая часть состоит из одного листа формата А1:

- структурная схема;

- принципиальная электрическая схема.

# 1. НЕОБХОДИМЫЕ ТЕОРЕТИЧЕСКИЕ ВОПРОСЫ ДЛЯ ВЫПОЛНЕНИЯ КУРСОВОЙ РАБОТЫ

### 1.1. Общие сведения об устройстве и работе ЭВМ

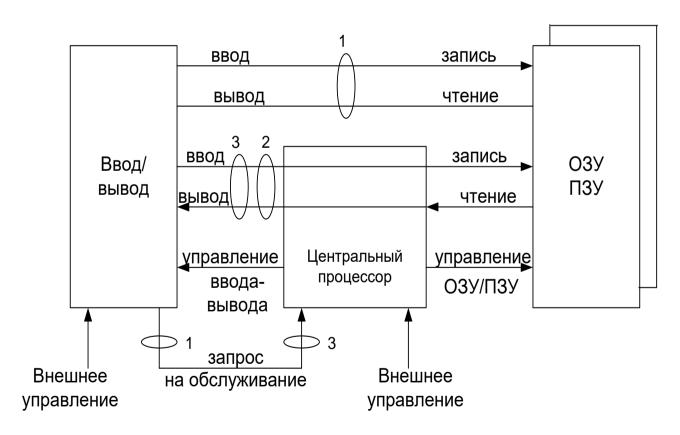

Структура любой ЭВМ может быть представлена упрощённой функциональной схемой, приведённой на рисунке 1. Схема включает в себя память, комбинационное АЛУ, устройство управления, устройства ввода-вывода.

Центральное место в структуре ЭВМ занимает память.

Именно здесь хранятся исходные данные для расчётов, программы обработки этих данных, а также промежуточные и окончательные результаты вычислений.

Память ЭВМ обычно делится на три части: ОЗУ, ПЗУ и сверхоперативное запоминающее устройство (СОЗУ).

ОЗУ и ПЗУ имеют адресную организацию. Доступ к их ячейкам памяти для записи и чтения информации осуществляется с помощью многоразрядного адреса, воздействующего на цепи группового управления.

СОЗУ представляет собой набор быстродействующих регистров, имеющих индивидуальное управление. Эти регистры обеспечивают работу АЛУ, фиксируя его входные и выходные коды.

Кроме того, СОЗУ используется для временного хранения данных в процессе их обработки.

Выполнение вычислительной машиной арифметических и логических операций над двоичными кодами реализовано в АЛУ.

Общее управление всеми элементами ЭВМ и взаимную синхронизацию их работы обеспечивает устройство управления, исполняющее команды человека-пользователя. Это могут быть команды внешнего управления, поданные, например, с пульта, либо команды программы, заранее занесённые в память.

Команды программы представляют собой двоичные коды, которыми зашифрованы приказы, исполнить те или иные операции математической обработки данных, пересылки данных, управления ходом исполнения программы.

Устройство управления должно автоматически выбирать команду из соответствующей ячейки памяти, исполнять её, выбирать следующую и т. д.

Обычно используется так называемый естественный порядок выполнения команд, когда последовательно друг за другом выполняются команды, занесённые в ячейки памяти с последовательно увеличивающимися адресами.

Адрес самой первой ячейки программы устанавливается при этом командой «сброс» внешнего управления.

Естественный порядок выполнения команд не требует каких-либо указаний в кодах команд, то есть используется по умолчанию.

Существуют специальные команды передачи управления, позволяющие нарушать естественный порядок либо безусловно, либо условно (в зависимости от признака результата выполненной АЛУ операции).

Такие команды каким-либо образом указывают устройству управления адрес следующей команды.

Обмен информацией между ЭВМ и внешней средой организуется через устройства ввода-вывода. Следует указать на возможность программного управления вводом-выводом и ввода-вывода по прерываниям.

В первом случае обмен информацией идёт по инициативе и под управлением программы.

Рис. 1. Функциональная схема ЭВМ

Во втором — устройство ввода-вывода само запрашивает обслуживание под действием внешних сигналов. Устройство управления, реагируя на этот запрос, прерывает выполнение основной программы ЭВМ и запускает заранее подготовленную программу обслуживания устройства ввода-вывода (программу обработки прерывания). По завершении ввода-вывода под управлением про-

граммы обработки ЭВМ вновь возвращается к выполнению основной программы с точки прерывания.

Устройство управления, АЛУ и регистры СОЗУ принято объединять в единый конструктивный блок, называемый центральным процессором.

#### 1.2. Особенности построения микро-ЭВМ

Вновь изобразим общую функциональную схему ЭВМ, используя понятие центрального процессора (рис. 2). Эта схема наглядно иллюстрирует систему внутренних информационных связей между устройствами ЭВМ.

В ЭВМ, созданных до появления микропроцессоров, как правило, организовывалась одновременная и параллельная работа центрального процессора, АЛУ, устройств ввода-вывода, ОЗУ и ПЗУ. Такая организация позволяет обеспечить высокую производительность ЭВМ, однако требует наличия многочисленных соединений процессора с другими устройствами как одиночными проводниками, так многоразрядными шинами связи.

Рис. 2. Функциональная схема ЭВМ, использующая центральный процессор

Обилие внешних связей препятствовало выполнению традиционных процессорных структур в виде одной или немногих интегральных схем, так как по

условиям производства и применения микросхема не могла иметь слишком большое число выводов.

Поэтому при миниатюризации центрального процессора пришлось отказаться от жёсткой, статической, выполненной раз и навсегда системы связей устройств вычислительной машины и организовать такую связь гибко, динамически с помощью общей для всех устройств шины (магистрали).

Магистральная организация обеспечивает все связи между устройствами ЭВМ, предусмотренные общей функциональной схемой, но не параллельно, как в схеме (рис. 3), а последовательно, с разделением во времени.

В каждый момент времени по общей шине взаимодействуют лишь два устройства вычислительной машины. Третье устройство отключено от шины с помощью выходов с открытым коллектором или тремя состояниями.

В рамках магистральной организации ЭВМ удалось разработать микроэлектронные центральные процессоры, реализованные на одной или нескольких микросхемах с числом выводов меньшим допустимого.

Такие микросхемы назвали микропроцессорами. ЭВМ с магистральной внутренней организацией и центральным процессором, построенным на микропроцессорах, стали называть микро-ЭВМ.

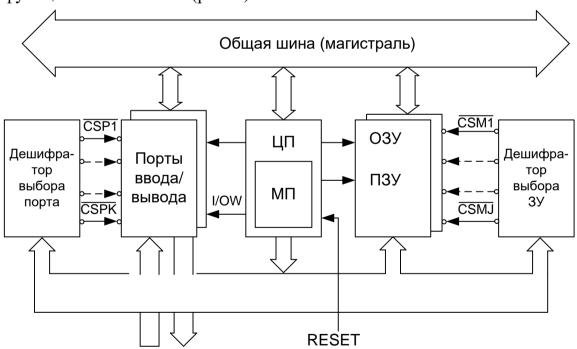

Функциональная схема ЭВМ с магистральной организацией приведена на рисунке 3.

Рис 3. Функциональная схема ЭВМ с магистральной организацией

Магистральная организация микро-ЭВМ исключает параллельную обработку информации разными устройствами машины.

Поэтому производительность микро-ЭВМ оказывается относительно низкой. За малые размеры аппаратуры здесь заплачено её быстродействием.

Следует указать, что за время, прошедшее с момента появления первого микропроцессора (1971 г.), технология производства и монтажа микросхем претерпела значительные изменения.

Соответственно увеличилось и допустимое число выводов микросхемы (от 40 в 1971 г. до нескольких сотен – в настоящее время).

Однако это обстоятельство не стимулировало отказа от магистральной организации микро-ЭВМ, так как такая организация оказалась очень удобной для модернизации, изменения состава устройств микро-ЭВМ и приспособления микро-ЭВМ к запросам конкретного пользователя.

Говорят, что магистральная организация обеспечивает открытость и гибкость построения микро-ЭВМ. Это очень полезные качества и, поэтому, несмотря на появление технических возможностей повышения производительности за счёт отказа от магистральной организации, производительность микро-ЭВМ повышают только за счёт увеличения быстродействия элементов и совершенствования процесса обработки информации в микропроцессоре (конвейерная обработка, кэширование, применение сопроцессоров).

#### 1.3. Архитектура простейшей микро-ЭВМ

В состав простейшей микро-ЭВМ входят центральный процессор, ОЗУ и ПЗУ, порты ввода и вывода, а также дешифраторы, осуществляющие выбор запоминающего устройства и порта ввода-вывода.

Построение микро-ЭВМ или, как часто говорят, её «архитектуру» поясняет функциональная схема (рис. 4).

Рис 4. Архитектура простейшей микро-ЭВМ

Рассматриваемая схема повторяет функциональную схему микро-ЭВМ с магистральной организацией (рис. 3), отличаясь более подробной детализацией. Так общая магистраль оказывается представлена здесь совокупностью трёх специализированных шин: шины данных, шины адреса и шины управления.

Шина данных (ШД) — является двунаправленной и предназначена для пересылки кодов обрабатываемых данных, а также машинных кодов команд между устройствами ЭВМ. Однонаправленная шина адреса (ША) несёт адрес (номер) той ячейки памяти или того порта ввода-вывода, который взаимодействует с микропроцессором. Шина управления несёт сигналы управления, обеспечивающие правильное взаимодействие блоков микро-ЭВМ друг с другом и с внешней средой. На рис. 2.4. эта шина представлена следующими сигналами:

MEMR – «чтение из памяти»; сигнал подтверждает приём байта данных из памяти в один из регистров микропроцессора;

MEMW – «запись в память»; сигнал извещает память о том, что микропроцессор выставил на шину данных байт, подлежащий записи в память;

I/OR — «чтение из порта ввода»; сигнал подтверждает приём байта данных из порта ввода в определённый регистр микропроцессора;

I/OW — «запись в порт вывода»; сигнал извещает порты вывода о том, что микропроцессор выставил на шину данных байт, подлежащий выводу через какой-либо из портов.

Рассмотренный набор сигналов шины управления является типовым. В конкретной микро-ЭВМ он может быть, как расширен, так и сужен.

Сигнал RESET – «сброс» является сигналом внешнего управления, он приводит микро-ЭВМ в исходное стартовое состояние.

Центральный процессор (ЦП) микро-ЭВМ выполнен на основе микропроцессора (МП). Кроме микропроцессора этот модуль содержит так называемые схемы обрамления. В состав обрамления входят разного рода вспомогательные устройства, обеспечивающие как работу микропроцессора, так и его связь с магистралью микро-ЭВМ.

Центральный процессор, ОЗУ, ПЗУ и порты ввода имеют выходы данных с тремя состояниями или открытым коллектором. Поэтому названные блоки могут либо отключаться (по выходу) от шины данных, либо, наоборот, захватывать эту шину. Центральный процессор управляет мультиплексированием шины данных по шине адреса с помощью дешифратора выбора ЗУ и дешифратора выбора порта. Дешифратор выбора ЗУ генерирует сигнал выбора соответствующего блока памяти (CSM1...CSMJ), анализируя старшие биты адреса ячейки памяти, выставленного микропроцессором на шине адреса. Младшие биты адреса обычно подаются параллельно на адресные входы всех блоков памяти. Рассмотренный метод гарантирует присвоение каждой из ячеек памяти своего единственного в системе, уникального адреса, а также непрерывность адресного пространства каждого из блоков памяти. Дешифратор выбора порта

генерирует сигнал выбора соответствующего порта (CSP1...CSPK), анализируя адрес порта, выставленный микропроцессором на шине адреса. Следует отметить, что сигналы выбора CSM1...CSMJ используются в микро-ЭВМ не только для мультиплексирования шины данных (то есть для разрешения чтения из того или иного блока), но и для демультиплексирования, то есть для разрешения записи в соответствующий блок.

Представленная схема имеет некоторые отступления от общей функциональной схемы ЭВМ (рис. 5). Так она не предусматривает прямого обмена информацией между портами ввода-вывода и памятью, минуя центральный процессор (этот вид обмена называют прямым доступом к памяти (ПДП), а также возможности прерывать выполнение основной программы в микро-ЭВМ для обслуживания запросов внешних устройств. Реализация названных возможностей требует введения в функциональную схему дополнительных устройств – контроллера ПДП и контроллера прерываний, связанных с соответствующими портами.

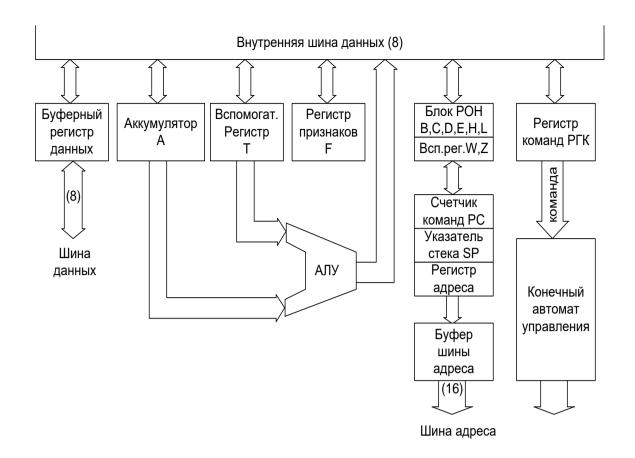

#### 1.4. Архитектура микропроцессора и центрального процессора

Будем считать, что простейшая микро-ЭВМ построена на основе микро-процессора INTEL8080A, который предназначен для арифметико-логической обработки восьмиразрядных кодов. Он способен взаимодействовать с памятью общим объёмом 64K, 256 портами ввода и 256 портами вывода. Взаимодействие обеспечивается двунаправленной восьмиразрядной шиной данных, шестнадцатиразрядной однонаправленной шиной адреса, а также рядом входных и выходных сигналов управления.

Построение микропроцессора или, как часто говорят, его «архитектуру» поясняет функциональная схема (рис. 5).

Часто считают, что эта схема включает в себя три специализированных процессора: операционный, выполняющий всю арифметико-логическую обработку; интерфейсный, обеспечивающий связь микропроцессора с внешней памятью и портами ввода вывода, и управляющий, обеспечивающий управление всеми узлами микропроцессора, приём и формирование управляющих сигналов.

Операционный процессор представлен здесь восьмиразрядным АЛУ и рядом восьмиразрядных регистров: регистром-аккумулятором A, регистром признаков или флагов F, регистрами общего назначения (POH) – B, C, D, E, H, L, вспомогательными регистрами T, W, Z.

Все перечисленные регистры, кроме вспомогательных, являются программно доступными.

Рис. 5. Архитектура микропроцессора INTEL8080A

Содержимое каждого из них доступно из программы пользователя, как для чтения, так и для записи.

Наиболее обширными функциями обладает аккумулятор А. Он используется микропроцессором при выполнении большинства команд. Регистры общего назначения могут использоваться для временного хранения как восьмиразрядных, так и шестнадцатиразрядных двоичных кодов. В последнем случае они объединяются в регистровые пары ВС, DE, HL. Регистры А и F могут рассматриваться как регистровая пара PSW, которая хранит в себе слово состояния программы PSW. Регистры W и Z тоже могут объединяться в регистровую пару.

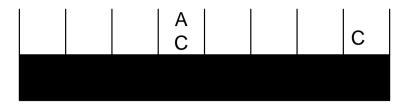

Остановимся подробнее на регистре признаков F. В нём запоминаются признаки результата, которые вырабатывает АЛУ микропроцессора при выполнении ряда команд. Формат регистра F представлен на рисунке 1.6.

Биты S, Z, AC, P, C – называют признаками результата или флагами. Если признак равен 1, говорят, что он установлен. Если признак равен 0, говорят, что он сброшен.

S=1, если результат отрицателен; Z=1, если в результате получен нулевой код. C=1, если при вычислении результата в АЛУ имел место перенос в старшие разряды или заём из старших разрядов. AC=1, если при вычислении

результата в АЛУ имел место межтетрадный перенос; P = 1, если код результата имеет чётное число единичных бит.

Рис. 6.Формат регистра признаков F

Интерфейсный процессор включает в себя шестнадцатиразрядные программно-доступные регистры — счётчик команд РС, указатель стека SP и программно-недоступный регистр адреса. Работа этого процессора сводится к установке нужного кода на шине адреса с помощью регистра адреса.

Источниками устанавливаемого кода могут быть регистры PC, SP, регистровые пары BC, DE, HL, WZ.

Счётчик команд РС обеспечивает выборку из памяти команд программы. Обычно он содержит в себе адрес следующего байтового слова программы, подлежащего выборке. Сразу же после выборки очередного байтового слова содержимое РС увеличивается на единицу.

Указатель вершины стека (указатель стека) SP используется для организации в ОЗУ микро-ЭВМ, так называемой стековой памяти. Функции этого регистра и особенности стековой памяти подробно рассмотрены ниже.

Управляющий процессор состоит из регистра команд РГК и конечного автомата управления, генерирующего в ответ на команду микропрограмму её исполнения. Этот процессор тактируется сигналами внешней синхронизации СLK1 и CLK2 и может устанавливаться в исходное состояние сигналом внешнего сброса RESET. Сигнал RESET также сбрасывает в ноль счётчик команд РС.

Управляющий процессор принимает и генерирует ряд сигналов управления. Наиболее важными из них являются импульсные сигналы DBIN — «приём» и WR — «выдача». Первый сигнал подтверждает приём байта данных с шины данных в буферный регистр данных микропроцессора. Второй сигнал извещает внешние устройства о том, что микропроцессор выставил на шину данных очередной байтовый код.

Следует отметить, что пара сигналов DBIN и WK не даёт возможности отличать обращения микропроцессора к памяти от обращений к портам вводавывода. Чтобы отличить эти обращения, приходится использовать дополнительную информацию о режиме работы микропроцессора. Такая информация

содержится в так называемом слове состояния микропроцессора SW. Оно выдаётся управляющим процессором на шину данных в отведённые для этого интервалы времени и стробируется выходным сигналом синхронизации SYNC.

Исполнение программы в микропроцессоре может быть прервано по запросу внешнего устройства сигналом прерывания INT.

Выводы шин адреса и данных микропроцессора выполнены как выходы с тремя состояниями. Эти выходы могут переходить в высокоимпедансное состояние в результате выполнения некоторых команд или под воздействием внешних сигналов.

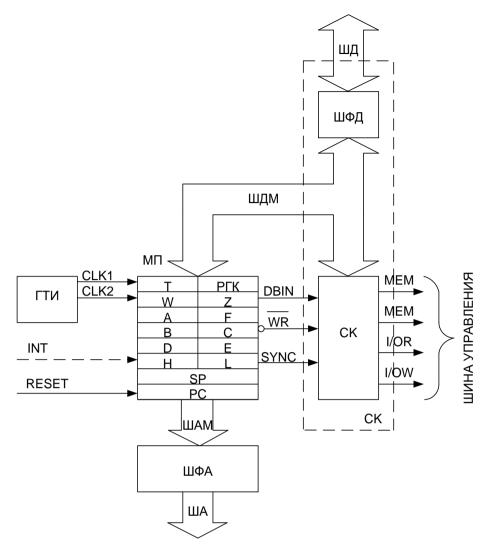

Функциональная схема центрального процессора, построенного на основе учебного микропроцессора, приведена на рис. 7. На этой схеме:

МП – микропроцессор (представлен множеством своих регистров);

ГТИ – генератор тактовых импульсов;

СК – системный контроллер;

ШФД – шинный формирователь шины данных;

ШФА – шинный формирователь шины адреса;

ШД – восьмиразрядная шина данных микро-ЭВМ;

ШДМ – восьмиразрядная шина данных микропроцессора;

ТТТА – шестнадцатиразрядная шина адреса микро-ЭВМ;

ШАМ – шестнадцатиразрядная шина адреса микропроцессора.

Тактовый генератор обеспечивает синхронизацию работы микропроцессора, шинные формирователи — усиление по мощности сигналов шин, а системный контроллер считывает слово состояния процессора SW и формирует сигналы шины управления MEMR, MEMW, IOR и IOW из выходных сигналов микропроцессора DBIN и WR с учётом этого слова.

Следует указать, что иногда включают в состав системного контроллера не только формирователь шины управления, но и шинный формирователь шины данных (показано пунктиром).

# 2. ПРИМЕРНОЕ СОДЕРЖАНИЕ ПОЯСНИТЕЛЬНОЙ ЗАПИСКИ

# 2.1. Пример построения структурной схемы разработанной системы

Так как по условию курсовой работы конкретно не задан тип измеряемой жидкости, то конкретно берём за основу проекта измерение расхода горячей воды на основе микропроцессорной техники в условиях котельной ОАО шахты «Западная», используемой для отопления АБК (административно-бытового Комбината).

Рис. 7. Архитектура центрального процессора

#### 2.2. Краткое описание тепловой сети

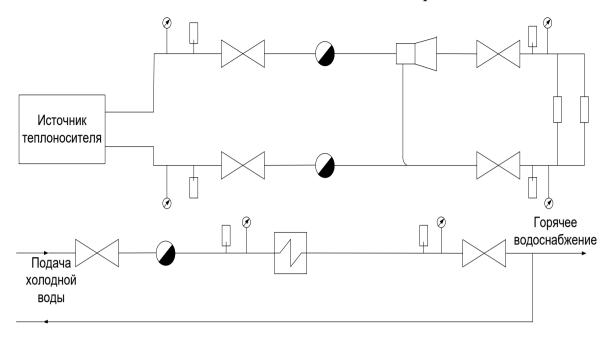

Из котельной, расположенной на территории ОАО шахта «Западная», на которой используется система водяного отопления с искусственной (насосной) циркуляцией, подогретая вода подаётся в систему отопления. Утечки воды из системы отопления пополняются подпиточной водой с помощью подпиточных насосов. В данном случае используется двухтрубная система водяного отопления с верхней разводкой магистральных труб. Холодная вода подаётся по отдельной линии насосами из артезианской скважины, затем подаётся в систему холодного водоснабжения. Схема системы горячего водоснабжения показана на рис. 8. В качестве топлива для котельной используется уголь, который по конвейерной линии технологического комплекса подаётся к котлам. Управление конвейерными линиями осуществляется из диспетчерского пункта шахты.

Главная задача регулирования систем отопления состоит в том, чтобы обеспечить отдачу теплоты нагревательными приборами, а температуру воздуха в отапливаемых помещениях поддерживать в соответствии с санитарными

нормами, В этом свете требуется регулировка следующих элементов: источника теплоснабжения, тепловых сетей, систем отопления и горячего водоснабжения.

Рис. 8. Схема горячего водоснабжения и отопления здания.

Согласно заданию, ограничимся измерением расхода жидкости на основе микропроцессорной техники.

#### 2.3. Описание структурной схемы разработанной системы

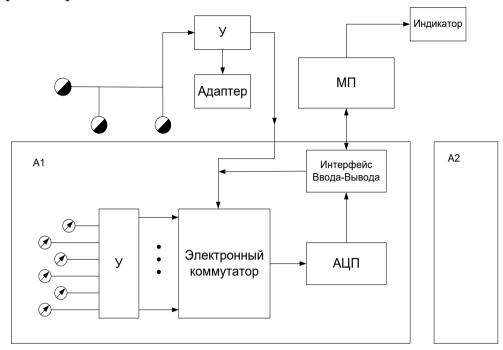

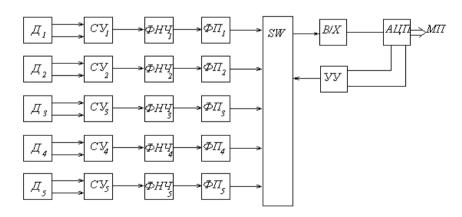

Структурная схема разработанной системы представлена на рисунке 9. Её основу составляет микропроцессорный блок, ультразвуковой расходомер УРСВ-010 в комплекте с преобразователем и усилителем и аналого-цифровой преобразователь, состоящий из электронного коммутатора, собственно преобразователя сигнала и интерфейса ввода-вывода.

Сигнал с датчиков расхода, установленных на прямой и обратной ветвях трубопровода, усиливается усилителем постоянного тока и поступает на электронный коммутатор. Электронным коммутатором управляет микропроцессор, в соответствии с программным решением. После коммутации сигнал поступает на АЦП, где из аналогового преобразуется в цифровой. Через интерфейс вводавывода сигнал подаётся на порт ввода микропроцессорного блока, откуда после обработки центральным процессором подаётся на дешифратор и затем на жидкокристаллический индикатор для численного представления или поступает на компьютер, где также представляется в числовой форме. На рисунке 9 показана структурная схема микропроцессорного блока, которая состоит из: интерфейсов ввода-вывода; контроллера прямого доступа к памяти; постоянного запоминающего устройства (ПЗУ); запоминающего устройства с произволь-

ной выборкой (ЗУПВ); микропроцессора: логики управления шиной и схемы генератора синхронизации.

Рис. 9. Структурная схема разработанной системы.

К микропроцессорным устройствам, подключаются самые разнообразные внешние устройства с помощью интерфейсов и контроллеров. Под контроллером понимаются схемы для инициирования приказов во ВУ (внешнее устройство) и восприятия состояния ВУ. Часто контроллер является составной частью ВУ.

Интерфейсом называются схемы для подключения ВУ с его схемой управления к соответствующей шине. Интерфейс должен выполнять некоторую комбинацию следующих функций:

- 1) передавать состояние ВУ в ЭВМ;

- 2) обеспечивать буферное хранение данных, вводимых из ВУ в ЭВМ;

- 3) принимать приказы от ЭВМ во ВУ;

- 4) обеспечивать буферное хранение данных, выводимых из ЭВМ во ВУ;

- 5) сигнализировать ЭВМ о завершении операции;

- 6) сигнализировать ЭВМ об ошибке, возникшей во время операции;

- 7) упаковывать биты в байты или слова для ввода и распаковывать их для вывода.

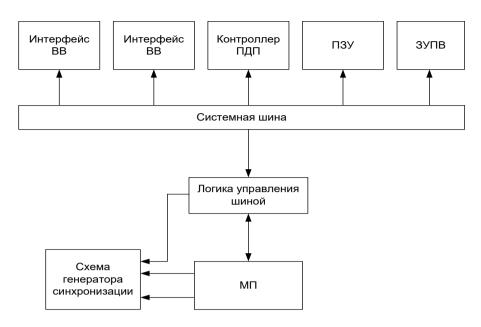

Системная шина состоит из линии данных и линии адреса. Линии данных используются для передачи информации. При взаимодействии с памятью этой информацией могут быть данные или команды, а при взаимодействии с ВУ – данные, состояние ВУ, приказы или информация о прерывании. Число линий, данных в шине определяет число передаваемых одновременно бит и поэтому

оказывает непосредственное влияние на скорость передачи информации, Микро-ЭВМ с n линиями данных обычно называют n-битной микро-ЭВМ.

Рис. 10. Архитектура ВВ микропроцессорного устройства

Каждая ячейка памяти или интерфейсный регистр ассоциируются с однозначной комбинацией бит, называемой адресом. Линии адреса предназначены для передачи комбинаций бит, которые дешифрируются как адреса подключёнными к шине интерфейсами. В многошинной архитектуре большинство ВУ подключается к различным шинам, называемым шинами ввода-вывода (ВВ), а шина для модулей памяти называется шиной памяти.

Постоянное запоминающее устройство (ПЗУ) выполняет только считывание. После записи содержимого его можно изменить только с помощью специального оборудования. Существует четыре основных типа ПЗУ, которые различаются по способу записи их содержимого. Команды и константы, которые не нужно изменять после установки, а также другая аналогичная информация, хранится в ПЗУ. Необратимый характер ПЗУ желателен в некоторых применениях, когда случайное изменение команды или другой информации в памяти может привести к катастрофическим последствиям. Кроме того, ПЗУ имеют большую плотность, высокое быстродействие и потребляют мало энергии. По этим причинам управляющую память реализуют в виде ПЗУ.

Запоминающее устройство с произвольной выборкой (ЗУПВ) обозначает память, которая выполняет операции считывания и записи. Этот термин традиционно используется для оперативной памяти. В некоторых применениях типа простых контроллеров можно обойтись без ЗУПВ, но во многих применениях приходится вводить и хранить больше данных, чем могут вместить регистры

ЦП или внутренняя память. В таких ситуациях для хранения данных до их обработки приходится применять ЗУПВ.

Даже в простых конфигурациях МП должен иметь логику, в основном содержащую схемы синхронизации и управления шиной. Схема синхронизации формирует импульсы синхронизации для микро-ЭВМ, а логика управления шиной подключает МП к системной шине и генерирует управляющие сигналы для координации действий шины в операции передачи данных или прерывания.

#### 2.4 Разработка и анализ алгоритма управления

Типовая последовательность разработки алгоритма управления содержит следующие этапы:

- 1. Анализ циклограммы работы объекта управления или блок-схемы. Если циклограмма работы или блок-схема отсутствуют, то, используя словесное описание алгоритма, необходимо их разработать.

- 2. Составление таблиц входных и выходных сигналов программируемого контроллера.

Таблицы должны содержать наименование и условное обозначение сигналов, их источник или приёмник, адресацию сигналов и их привязку к контактам разъёмов контроллера.

- 3. В некоторых случаях является полезным описать алгоритм (циклограмму) уравнениями алгебры логики.

- 4. Если язык программирования выбранного контроллера относится к группе языков релейно-контактных схем (РКС или по международной классификации LD), то целесообразно начертить релейно-контактный эквивалент алгоритма. Это облегчит разработку программы управления для программируемого контроллера и её чтение.

По результатам выполнения перечисленных этапов подготавливается информация для разработки программы управления программируемого контроллера, а в графической части изображается электрическая схема подключения к контроллеру информационных (датчиков) и исполнительных устройств.

# 2.5 Разработка программы управления

Завершающим этапом проектирования программно-логической подсистемы управления дискретным процессом является написание программы управления для программируемого контроллера.

Характерной чертой программируемых контроллеров по сравнению с обычными офисными компьютерами состоит не только в ориентации на работу с платами ввода-вывода, но и в преимущественном использовании языков технологического программирования. Как правило, на предприятиях с контролле-

рами работают не программисты, а специалисты-технологи, хорошо знающие специфику объектов управления и технологического процесса. Для написания программы управления используются такие языки как язык релейноконтактных схем, функциональных блоков и т. д.

Накопленный многими фирмами опыт программирования программируемых контроллеров обобщён в виде стандарта IEC61131, где определены пять языков программирования контроллеров: SFC — последовательных функциональных схем, LD — релейных диаграмм, FBD — функциональных блоковых диаграмм, ST — структурированного текста, IL — инструкций.

Наиболее известными реализациями этого стандарта являются пакеты UltraLogik и CoDeSys.

# 2.6 Расчёт основных узлов канала сбора аналоговых данных микропроцессорной системой

#### 2.6.1 Разработка структурной схемы устройства

Изначально следует определиться с типом мультиплексирования каналов сбора данных. Как следует из теоремы Котельникова — для того чтобы из дискретных уровней можно было восстановить исходный аналоговый сигнал, необходимо, чтобы частота квантования минимум в два раза превышала наивысшую частоту спектра сигнала. С учётом некоторого коэффициента запаса частота квантования выбирается в пять раз больше максимальной частоты спектра сигнала:

$$f_K = (3...5) F_{\text{max}} = 4 F_{\text{max}} = 4 \cdot 20 = 80, [\Gamma_{\text{II}}].$$

Исходя из требуемой в условии разрядности выходной комбинации, выбирается 12-разрядный АЦП К572ПВ1А, обладающий временем преобразования 170 мкс и на вход которого можно подавать максимальное напряжение 10 В.

Таким образом с помощью данного АЦП можно опрашивать состояние сигнала с максимальной частотой  $1/t_{\text{ацп}}$ . Для аналогового мультиплексирования необходимо, чтобы частота опроса состояния на входе АЦП была больше либо равна произведению числа каналов на частоту квантования:

$$nf_{K} \le \frac{1}{t_{aun}};$$

$$5 \cdot 80 \le \frac{1}{170 \cdot 10^{-6}}; \ 400 \ \Gamma \text{L} \le 5882 \ \Gamma \text{L}.$$

Таким образам аналоговое мультиплексирование вполне удовлетворит нуждам проектируемого устройства.

Рис. 11. Схема включения микросхемы К572ПВ1

АЦП имеет несимметричный аналоговый вход, а датчик — симметричный выход. Отсюда ясно, что в состав аналогового тракта должен входить дифференциальный усилитель, подключённый к выходу датчика. Назовем этот усилитель согласующим (СУ).

Наибольшая точность преобразования аналогового сигнала в цифровой код получается, когда используется вся шкала АЦП, т. е. в том случае, когда:

$$U_{ex.\max}^{AU\Pi} = III_{AU\Pi} = 10 \text{ B},$$

где  $U_{ax\, {

m max}}^{AU\Pi}$  — максимальное значение сигнала на аналоговом входе АЦП,  $U_{AU\Pi}$  — шкала АЦП.

Максимальная величина ЭДС  $e_{c \max}$  датчика намного меньше шкалы АЦП, поэтому аналоговый тракт должен обладать коэффициентом усиления не менее чем:

$$K_Z = \alpha \frac{III_{AIIII}}{e_{c \text{max}}} = 1,3 \cdot \frac{10}{0,08} = 163,$$

где  $\alpha$  – коэффициент запаса по усилению.

Из задания на проект известно, что наряду с полезным сигналом действует синфазная помеха. Для исключения её влияния аналоговый тракт должен иметь коэффициент ослабления синфазного сигнала (КОСС):

$$\begin{split} KOCC &= \frac{2 \cdot U_{\textit{cum}\phi}}{e_{\textit{c} \, \text{min}}} \,, \\ e_{\textit{c} \, \text{min}} &= e_{\textit{c} \, \text{max}} \cdot 10^{-D/20} = 0,08 \cdot 10^{-30/20} = \ 15,81 \cdot 10^{-4} \,, \\ KOCC &= \frac{2 \cdot 1,0}{15,81 \cdot 10^{-4}} = 1265 \,. \end{split}$$

Зависимость ЭДС датчика от измеряемой величины является не линейной. В связи с этим требуется включение в состав измерительного тракта функционального преобразователя, обеспечивающего линеаризацию характеристики датчика.

Из задания на проект известна полоса частот спектра полезного сигнала. Это даёт возможность сформулировать технические требования к фильтру низких частот по полосе пропускания: граничная частота фильтра  $f_{\phi H^{\prime}}=f_{B}$ , где  $f_{B}=20(\Gamma \mu)$  — верхняя частота спектра сигнала датчика.

В задании на проект не оговорены требования к АЧХ фильтра, поэтому тип фильтра низких частот (ФНЧ) выбирается RC-фильтр типа Баттерворта 2-го порядка.

Преимущества применения активных RC-фильтров по сравнению с LC-фильтрами – хорошая равномерность AЧX в полосе пропускания и хорошая скорость спада на переходном участке: практически полная развязка входных и выходных цепей, малые габариты и т. д.

Если фильтр выполняется в виде отдельного функционального узла, то его необходимо включать обязательно до нелинейного устройства. В противном случае высокочастотные помехи наводки (с ними практически всегда приходится иметь дело) могут быть трансформированы в область спектра полезного сигнала.

Производим выбор структурной схемы аналогового тракта, которая имеет следующий вид:

Рис. 12. Структурная схема аналогового тракта

Где CY – согласующий усилитель;

$\Phi H H - фильтр низких частот;$

$\Phi\Pi$  – функциональный преобразователь;

*УВХ* – устройство выборки-хранения;

$AU\Pi$  — аналогово-цифровой преобразователь; VV — устройство управления.

# 2.6.2 Определение технических требований к функциональным узлам системы

Расчёт технических требований будем производить в обратном порядке прохождения аналогового сигнала.

Устройство выборки и хранения. Основными техническими характеристиками УВХ являются:

1. Коэффициент передачи в момент окончания выборки

$$k_{yBX} = \frac{U_{gblX}^{yBX}}{U_{gr}^{yBX}}.$$

- 2. Максимальные значения входного  $U_{\rm \it ex\,max}^{\it \it VBX}$  и выходного  $U_{\rm \it eblx\,max}^{\it \it VBX}$  напряжений.

- 3. Входное  $R_{gx}^{yBX}$  и выходное  $R_{gy}^{yBX}$  сопротивление по аналоговому сигналу.

- 4. Относительные ошибки выборки  $\delta_{sb\delta}^{VBX}$  и  $\delta_{xpah}^{VBX}$  хранения.

- 5. Форма и параметры сигнала на управляющем входе УВХ.

- 6. Напряжение источников питания УВХ.

Так как существует большая неопределённость выбора указанных параметров УВХ, то их нужно задать, используя практический опыт построения подобных устройств и инженерную интуицию. Следует помнить, что в случае невозможности реализации УВХ с заданными наперёд характеристиками, возможен этап коррекции технического задания. Это, собственно, обычный (стандартный) путь решения инженерных и исследовательских задач.

В первую очередь можно задаться  $k_{y_{BX}} = 1$ . Затем найдём максимальное значение напряжения входного аналогового сигнала:

$$U_{\rm ex\,max}^{\rm VBX} = U_{\rm ebx\,max}^{\rm VBX} = U_{\rm ex\,max}^{\rm AUII} = III_{\rm AUII} = 10\,{\rm B}\,.$$

Зная, что современные методы построения УВХ дают возможность реализации относительных ошибок  $\delta^{\mathit{VBX}}_{\mathit{выб}}$  и  $\delta^{\mathit{VBX}}_{\mathit{xpah}}$  до  $10^{-4}$  и ниже, можно установить требования к допустимой погрешности:

$$\delta_{\text{выб}}^{\text{VBX}} = \delta_{\text{хран}}^{\text{VBX}} \le 10^{-3}$$

.

Ориентируясь на выполнение аналогового тракта на операционных усилителях (ОУ), задаются стандартной величиной напряжения источников питания:

$$E_{U1} = +15 (B);$$

$E_{U2} = -15 (B).$

Как известно, в схемах на ОУ достаточно легко реализуются большое входное сопротивление (до единиц мегом) и малое выходное сопротивление (менее десятков – сотен Ом), поэтому устанавливаем требования:

$$R_{\rm ex}^{{\it VBX}} \ge 1$$

кОм,  $R_{\rm ebx}^{{\it VBX}} \le 10$  Ом.

Длительность импульсов управления и период их следования оговорены в техническом задании на проект. Подлежит определению величины времени хранения:

$$t_{xp} = 2 \cdot t_{aun} = 340 \cdot 10^{-3}$$

, (c)

и амплитудные значения импульса и впадины на управляющем входе УВХ.

При реализации управляющего тракта полностью на ОУ выбираем:

$$U_{y \text{max}}^{VBX} = 12 \text{ (B)}, \qquad U_{y \text{min}}^{VBX} = -12 \text{ (B)}.$$

При расчёте принципиальной схемы эти данные будут учтены.

Функциональный преобразователь. Основной характеристикой функционального преобразователя является зависимость выходного напряжения  $U_{\scriptscriptstyle 6blx}^{\Phi H}$  от входного  $U_{\scriptscriptstyle 6x}^{\Phi H}$  :

$$U_{\text{\tiny GBJX}}^{\Phi\Pi} = f(U_{\text{\tiny ex}}^{\Phi\Pi}).$$

Зависимость ЭДС датчика задана аналитическим выражением:

$$e=0,4\cdot q2,$$

где q – измеряемая величина.

Пределы измеряемой величины можно найти, решив систему уравнений:

$$e = 0.4 \cdot q2 \ (qmin);$$

$e = 0.4 \cdot q2 \ (qmax).$

Находим что: qmin = 0,1 (B), qmax = 0,25 (В).

Найдём зависимость  $U_{\rm \tiny 6blX}^{\Phi\Pi}=f(U_{\rm \tiny 6x}^{\Phi\Pi})$  графическим путём. Для этого построим график зависимости.

$$e = 0.4 \cdot q2 \cdot K$$

.

Затем строим симметричную относительно оси кривую, она и будет искомой передаточной характристикой функционального преобразователя. Далее аппроксимируем кривую ломаной и определяем графическим путём координаты точек излома  $U_{\mathit{suxj}}^{\phi\Pi}$ , и требуемый коэффициент усиления на участках по формуле:

$$K_{j} = \frac{U_{\text{вых } j}^{\Phi \pi} - U_{\text{вых } j-1}^{\Phi \pi}}{U_{\text{вх } j}^{\Phi \pi} - U_{\text{вх } j-1}^{\Phi \pi}}.$$

Необходимые построения приведены на рисунке 6.

Найдём коэффициенты усиления на каждом кусочно-линейным отрезке:

$$K_{1} = \frac{1,3-0,1}{4,8-3,3} = 0,8,$$

$$K_{2} = \frac{3,7-1,3}{6,7-4,8} = 1,26,$$

$$K_{3} = \frac{6-3,7}{8,1-6,7} = 1,64,$$

$$K_{4} = \frac{10-6}{10-8,1} = 2,1.$$

Выходное сопротивление функционального преобразователя

$$R^{\Phi\Pi} < 0.1, \quad R^{YBX} = 0.1$$

Входное сопротивление ФУ

$$R^{\phi_{\Pi}} = (10 \cdot 103 - 1 \cdot 106) \text{ Om.}$$

Фильтр нижних частот. Основными характеристиками и параметрами фильтра нижних частот являются:

- 1. Верхняя граничная частота  $f_{B}$ .

- 2. Неравномерность АЧХ в полосе пропускания.

- 3. Скорость спада частотной характеристики на переходном участке АЧХ.

- 4. Коэффициент передачи  $K_{\phi H Y}$  по напряжению в полосе пропускания.

При использовании фильтров Баттерворта неравномерность АЧХ в полосе пропускания задавать не требуется, т. к. она получается минимальной.

Скорость спада выберем порядка 12 дБ/октаву.

Фильтры Баттерворта, выполненные на ОУ, имеют  $K_{\phi H Y} = 1,35 \div 1,5$ . Зададимся  $K_{\phi H Y} = 1,5$ . Исходя из этого, можно определить требования к максимальной величине входного напряжения:

$$U_{ex\,\text{max}}^{\phi H Y} = \frac{U_{ex}^{\phi y}}{K_{\phi H Y}} = \frac{III_{AIII}}{K_{\phi H Y}} = \frac{10}{1.5} = 6.7, \text{ B}.$$

Входное и выходное сопротивления выберем

$$R_{ex}^{\phi HY} = 500$$

, kOm;,  $R_{ehx}^{\phi HY} = 50$  Om.

Согласующий усилитель должен обладать номинальным коэффициентом усиления разностного сигнала не менее чем:

$$K_{CV_{HOM}} \ge \frac{K_Z}{K_{\phi HY}} = \frac{163}{1,5} = 108,7$$

.

Этот коэффициент изменяется в пределах ±10 дБ, т. е.

$$0,316 \cdot K_{CV_{HOM}} \le K_{CV} \le 3,16 \cdot K_{CV_{HOM}},$$

$34,57 \le K_{CV} \le 343,49.$

Коэффициент ослабления синфазной помехи должен быть не менее чем (расчёт приведён выше):  $KOCC \ge 1265$ .

Входное сопротивление  $R_{\rm sx}^{\rm CV}$  выберем из соотношения:

$$R_{\rm gx}^{\rm CV} \ge \Delta R_{\rm o} \cdot 10^{D/20} - R_{\rm o} = 87 \cdot 10^{40/20} - 46,5 = 8653,5 \,\,{\rm Om}\,.$$

Выходное сопротивление согласующего усилителя:

$$R_{\text{blux}}^{CV} \le 0.08 \cdot R_{\text{blux}}^{\Phi HQ} = 0.08 \cdot 500 \cdot 10^3 = 40 \text{ kOm}$$

.

#### 2.6.3 Выбор и расчёт принципиальных схем основных блоков

# 2.6.3.1 Согласующий усилитель

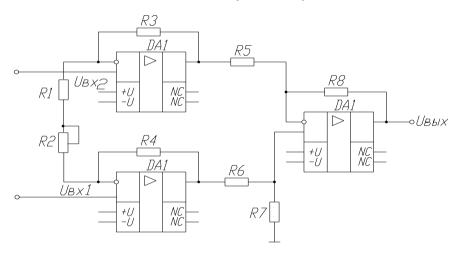

Рис. 13. Согласующий усилитель

Согласующий усилитель выполняет несколько функций:

- усиление сигнала до максимального входного напряжения АЦП;

- ослабление синфазной помехи;

- согласование симметричных выходов датчика с несимметричными входами функциональных блоков аналогового тракта.

Расчёт СУ начнём с выбора операционного усилителя (ОУ). Критериями выбора является возможность удовлетворения следующих неравенств:

Дрейф нуля в рабочем диапазоне температур (принимается 0...80°C):

$$\begin{split} \frac{dU_{CM}}{dT} \cdot \Delta T < &(0.1 \div 0.5) \cdot e_{c \min}, \\ \frac{dU_{CM}}{dT} \cdot \Delta T < &0.5 \cdot 8.89 \cdot 10^{-4}, \end{split}$$

$$\frac{dU_{CM}}{dT} \cdot \Delta T < 0,0004 \ B.$$

Входное дифференциальное сопротивление:

$$\begin{split} R_{ex.\partial u\phi} > & (1 \div 10) \cdot R_{\Gamma} \,, \\ R_{ex.\partial u\phi} > & 10 \cdot 15 \,\, \text{Om} \,, \\ R_{ex.\partial u\phi} > & 150 \,\, \text{Om}. \end{split}$$

Необходимый коэффициент ослабления синфазного сигнала:

$$KOCC = 1799$$

,

$KOCC (дБ) = 20 \cdot \lg KOCC = 20 \cdot \lg 1265 = 62 дБ$ .

Для построения схемы согласующего усилителя будем использовать операционный усилитель КР140УД7 с такими характеристиками:

- максимальный коэффициент усиления Ku = 50~000;

- коэффициент ослабления синфазного сигнала КОСС = 70 дБ;

- максимальное синфазное входное напряжение  $U_{cund max} = 11 \text{ B};$

- максимальное входное напряжение  $U_{ex\ max} = 12 \text{ B};$

- максимальное выходное напряжение  $U_{\text{вых max}} = 11,5 \text{ B};$

- напряжение питания  $U_n = \pm 15 \text{ B}$ ;

- максимальный выходной ток  $I_{\text{вых max}} = 20 \text{ мA};$

- входные токи  $I_{ex} = 200$  нА.

Выбранная микросхема удовлетворяет предъявленным к ней требованиям.

Для достижения наибольшего ослабления синфазной помехи коэффициент усиления первой ступени усиления на DA1, DA2 желательно брать наибольшим (т. е. реализовать на ней основное усиление сигнала), а коэффициент усиления разностного усилителя на ОУ DA3 принять равным единице. В этом случае резисторы R5чR8 получатся одного номинала, а, следовательно, облегчается их подбор по требуемому допуску и температурному коэффициенту. Расчёт элементов схемы начинаем с каскада на DA3.

Зададим номиналы резисторов в пределах

$$R_{\min} < R_5 = R_6 = R_7 = R_8 < \left(2 \cdot 10^3 \div 10^6\right) \text{ Ом},$$

где  $R_{\min} = \frac{U_{ex\,\max}}{I_{ex\,v\,\max}} = \frac{12}{20 * 10^{-3}} = 640 \text{ Ом},$

где  $U_{\mathit{ex\,max}}$  – максимальное входное напряжение операционного усилителя,

$I_{\text{вых max}}$  — максимальный выходной ток операционного усилителя.

Выбираем номиналы R5, R6, R7, R8 равными 1 кОм. Резисторы R3 и R4 выбираем равными 20 кОм. Для определения сопротивления резистора R2, воспользуемся формулами:

$$R_{\min} = \frac{U_{\text{ex max}}}{I_{\text{eblx max}}} = \frac{12}{20 \cdot 10^{-3}} = 640 \text{ Om},$$

$$R_{\max} = 2 \cdot \text{R3}/(K_{\text{cy min}} - 1) = 2 \cdot 20 \cdot 103/(10,97 - 1) = 4 \text{ kOm},$$

$$R_{\min} = 2 \cdot \text{R3}/(K_{\text{cy max}} - 1) = 2 \cdot 20 \cdot 103/(109,7 - 1) = 0,37 \text{ kOm}.$$

Так как резистор  $R1 = R_{min}$ , то задаёмся номинальным значением R1 - 390 Ом.

$$R2 = R_{max} - R_{min} = 3,63$$

кОм.

Выбираем резистор R2 номиналом 3,9 кОм с учётом допустимых отклонений в значениях резисторов R1 и R2.

Допуск на относительный разброс номиналов резисторов (кроме  $R_1$  и  $R_2$ ), % определяем по формуле:

$$\delta_R = \frac{K_{cy \min} \cdot 100\%}{2 \cdot KOCC_{TDEG}} = \frac{10,97 \cdot 100\%}{2 \cdot 62} = 10,33\%.$$

При определении номиналов резисторов учитываем, что резисторы R5чR8 определяют величину входного сопротивления каскада по инвертирующему и неинвертирующему входам и являются фактическими нагрузками ОУ, DA1, DA2. Кроме того, применение высокоомных резисторов R5чR8 приводит к повышенному дрейфу выходного напряжения из-за некомпенсируемой разности входных токов  $\Delta Iex$  (паспортный параметр ОУ).

Выбираем резисторы:

$R_1 = \text{C2-33H-0,25-390 Om} \pm 10\%;$

$R_2 = \text{C2-33H-0,25-3,9} \text{ кОм} \pm 10\%;$

$R_3 = \text{C2-33H-0,25-20 kOm} \pm 10\%;$

$R_4 = \text{C2-33H-0,25-20 кОм} \pm 10\%;$

$R_5 = \text{C2-33H-0,25-1 kOm} \pm 10\%;$

$R_6 = \text{C2-33H-0,25-1 kOm} \pm 10\%;$

$R_7 = \text{C2-33H-0,25-1 kOm} \pm 10\%;$

$R_8 = \text{C2-33H-0,25-1 kOm} \pm 10\%.$

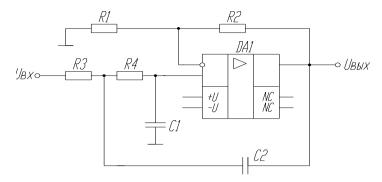

# 2.6.3.2 Фильтр низких частот

Фильтр низких частот (рис. 14) выполнен по схеме Баттерворта второго порядка.

Верхняя граничная частота определяется по формуле:

$$f_{\rm rp} = \frac{1}{2 \cdot \pi \cdot R \cdot C}.$$

Рис. 14. Фильтр низких частот

Целесообразно задаться сначала величиной ёмкости из ряда стандартных значений, затем рассчитать величины резисторов:

$$R = \frac{1}{2 \cdot \pi \cdot f_{en} \cdot C}.$$

Величину ёмкости С следует выбрать такой, чтобы получить значения резистора R в пределах  $10{\text -}100$  кОм. Выбираем ёмкость C=0,1 мк $\Phi$ .

$$R = \frac{1}{2 \cdot 3.14 \cdot 25 \cdot 0.1 \cdot 10^{-6}} = 63694 \,\text{Om}.$$

Выбираем номинал R = 6.8 кОм. С целью уменьшения влияния разности входных токов ОУ должно выполняться равенство:

$$\frac{R1 \cdot R2}{R1 + R2} = 2R.$$

В то же время для получения необходимой АЧХ:

$$R2 = (2-\alpha) \cdot R1$$

.

Решая систему уравнений, получаем значения R1 = 24,57 кОм (выбираем номинал 27 кОм), R2 = 14,4 кОм (выбираем номинал 15 кОм). По полученным параметрам рассчитываем коэффициент усиления фильтра низких частот:

$$K_{\Phi H \Psi} = 1 + \frac{R2}{R1} = 2.8.$$

Выбираем резисторы:

$$R_1$$

= C2-33H-0,25-27 кОм ± 5% C<sub>1</sub> K73-11-63 B-0.15 мкФ ± 20%;

$R_2$  = C2-33H-0,25-15 кОм ± 5% C<sub>2</sub> K73-11-63 B-0.15 мкФ ± 20%;

$R_3$  = C2-33H-0,25-68 кОм ± 5%;

$R_4$  = C2-33H-0,25-68 кОм ± 5%.

# 2.6.3.3 Расчёт устройства выборки и хранения

В качестве устройства выборки/хранения можно использовать микросхему КР1100СК2, имеющую такие характеристики:

- время выборки 5-10 мкс;

- коэффициент усиления  $K_{vex} = 1$ ;

- напряжение питания  $U_n = \pm 12$  В;

- напряжение управления  $U_{ynp} = 2.7 \text{ B};$

- скорость изменения выходного напряжения  $\Delta U = 0.25 \text{ B/c}$ ;

- максимальное входное напряжение  $U_{ex} = 10 \text{ B}$ ;

- напряжение смещения  $U_{cm} = 5-30$  мВ.

При подключении к данной микросхеме конденсатора ёмкостью 1 000 пФ, можно получить время хранения равное 10 мкс.

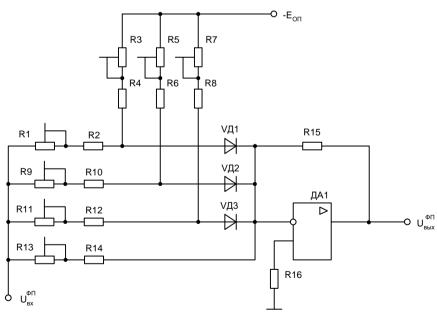

#### 2.6.3.4 Расчёт функционального преобразователя

Схема функционального преобразователя, у которого с ростом входного сигнала возрастает коэффициент усиления приведена на рисунке 15.

При  $U_{\text{вх}}^{\text{фп}} < U_{\text{вх1}}^{\text{фп}}$  диоды VD1 - VD3 закрыты отрицательным смещением резистивных деталей. Коэффициент усиления по напряжению

$$K1 = \frac{R15}{R13 + R14}$$

выбирая R15 = 10кОм, получаем,

$$R13 + R14 = \frac{R15}{K1} = \frac{10 \cdot 10^3}{0.8} = 12.5$$

, кОм.

Выбираем R14 = 10 кОм, R13 = 5,1 кОм.

Рис. 15. Принципиальная схема функционального преобразователя

С ростом входного напряжения повышаются потенциалы анодов диодов, в то время как потенциалы их катодов остаются неизменными и близкими к нулю. При  $U_{\text{вх}}^{\text{фп}} = U_{\text{вх1}}^{\text{фп}}$  открывается диод VD3, коэффициент усиления возрастает и становится:

$$K2 = \frac{R15}{(R13 + R14) / /(R11 + R12)} = 1,26.$$

Получаем R11 + R12 = 16,6 кОм. Выбираем R12 = 13 кОм, R11 = 5,1 кОм.

При  $U_{\text{вх}}^{\varphi_{\text{п}}} = U_{\text{вх2}}^{\varphi_{\text{п}}}$  открывается диод VD2, коэффициент усиления возрастает и становится:

$$K3 = \frac{R15}{(R13 + R14) / (R11 + R12) / (R9 + R10)} = 1,64.$$

Получаем R9+R10=10,25 кОм. Выбираем R10=8,2 кОм, R9=2,2 кОм. При  $U_{\rm Bx}^{\rm dpn}=U_{\rm Bx3}^{\rm dpn}$  открывается диод VD1, коэффициент усиления возрастает и становится.

При  $U_{\text{вх}}^{\phi \text{п}} = U_{\text{вх4}}^{\phi \text{п}}$  открывается диод VD1, коэффициент усиления возрастает и становится:

$$K4 = \frac{R15}{(R13 + R14) / /(R11 + R12) / /(R9 + R10) / /(R1 + R2)} = 2,1.$$

Получаем R1 + R2 = 19,3 кОм. Выбираем R2 = 16 кОм, R1 = 6,2 кОм.

Рассчитываем значение сопротивлений делителя. Для этого зададимся опорным напряжением, равным  $E_{on}=10~\mathrm{B}$ . Величины входных напряжений необходимых для поочередного отпирания диодов возьмём из графика  $U_{\rm Gblx}=f_{\rm (Uex)}$ . Расчёт сопротивлений делителя производится из условия:

$$Ron = \frac{Eon \cdot Rex}{Uex}.$$

Таким образом сопротивления делителя находятся как:

$$R7 + R8 = \frac{Eon \cdot (R11 + R12)}{Uex1} = \frac{10 \cdot 18, 1 \cdot 10^3}{3,3} = 82 \text{ kOm}.$$

Выбираем R8 = 68 кОм, R7 = 22 кОм.

$$R5 + R6 = \frac{Eon \cdot (R9 + R10)}{U_{ex2}} = \frac{10 \cdot 10, 4 \cdot 10^3}{4,8} = 20 \text{ kOm}.$$

Выбираем R6 = 15 кОм, R5 = 6.8 кОм.

$$R3 + R4 = \frac{Eon \cdot (R1 + R2)}{Uex3} = \frac{10 \cdot 22, 2 \cdot 10^3}{6,7} = 28 \text{ kOm}.$$

Выбираем R4 = 22 кОм, R3 = 9,1 кОм.

#### 2.6.3.5 Расчёт управляющего тракта

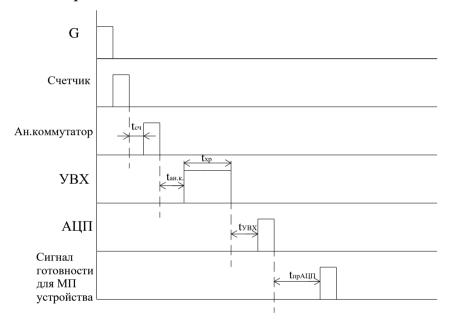

Блок управления необходим для управления работой всего устройства. Он синхронизирует работу отдельных блоков. Для обеспечения нормальной работы системы сбора аналоговых данных необходимо поочерёдно подавать сигналы с генератора на вход счётчика, аналогового коммутатора, УВХ, АЦП, буфера хранения и сигнал готовности для микропроцессорного устройства. Частота работы генератора определяется частотой опроса датчиков. Сигналы на входы блоков должны подаваться с определённой задержкой, равной времени преобразования предыдущего устройства. Принцип работы блока управления отображён на диаграмме.

Рисунок 16 – Принцип работы блока управления

где  $t_{cy}$  — время преобразования счётчика;  $t_{ah.\kappa}$  — время преобразования аналогового коммутатора;  $t_{xp}$  — время хранения данных в УВХ;  $t_{yBX}$  — время преобразования в УВХ;  $t_{np.AUII}$  — время преобразования АЦП.

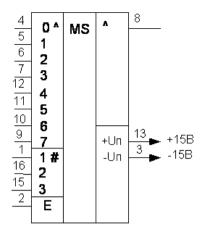

В качестве аналогового коммутатора воспользуемся микросхемой КР590КН6. Справочные данные:  $U_{num}=\pm$  15B;  $U_{\kappa om}=\pm$  15B;  $I_{\kappa om}=20$  мA;  $t_{\kappa \kappa n}=0.3$  мкс;  $U_{\kappa \kappa n}=0...0,8$  B;  $U_{\kappa \kappa n}=4...16,5$  В (рис. 17).

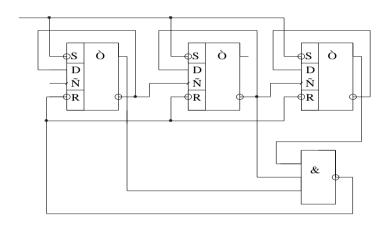

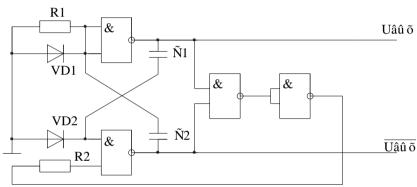

Для формирования номера опрашиваемого датчика будет использоваться счётчик на основе D-триггеров, показанный на рисунке 18.

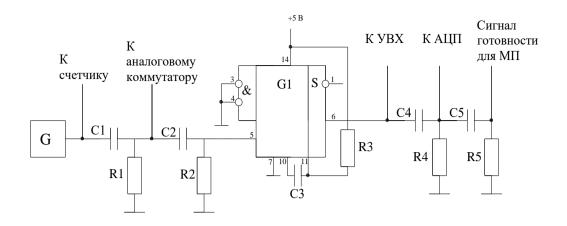

Схема блока управления изображена на рисунке 19. Она состоит из: генератора прямоугольных импульсов; цепей задержки, сформированных на базе RC-цепочек; а также из одновибратора, который используется как расширитель импульса для УВХ.

Рисунок 17 – Аналоговый коммутатор

Рисунок 18 – Счётчик с коэффициентом пересчёта 5

Частота опроса датчиков составляет  $f=120~\Gamma$ ц. Длину импульса возьмём равную 1 мкс. Тогда:

$$t_{II} = R_1 \cdot C_1 \cdot \ln(U_1 / U_{nop}),$$

$$1 \cdot 10^{-6} = R_1 \cdot C_1 \cdot \ln(2, 4 / 1, 25).$$

Выбираем  $R_1 = 2,2$  кОм, а  $C_1 = 765$  пФ.

$$t_{\Pi} = R_2 \cdot C_2 \cdot \ln(U_1 / U_{nop}),$$

$$1999 \cdot 10^{-6} = R_2 \cdot C_2 \cdot \ln(2, 4/1, 25).$$

Выбираем R2 = 22 кОм,  $\underline{C}2 = 0,1302$  мкФ.

Рисунок 19 – Схема блока управления

В качестве генератора импульсов будем использовать схему, приведённую на рисунок 20.

Рисунок 20 – Схема генератора прямоугольных импульсов

Для обеспечения подачи импульса на УВХ равного  $t_e = 10$  мкс будем использовать одновибратор на основе микросхемы К155АГ1. Для этой микросхемы длительность импульса обеспечивается из условия  $t_{\rm вых} = R_3 \cdot C_3 \cdot \ln 2$ . Поэтому выбираем C3 = 650 мкФ, а R3 = 22 кОм.

Расчёт RC-цепочек.

Время задержки сигнала на вход аналогового коммутатора равно 500 нс.

$$t_{cy} = R_1 \cdot C_1 = 500 \cdot 10^{-9}$$

.

Выбираем  $R_1$  = 2,2 кОм,  $C_1$  = 227 пФ.

Время задержки сигнала на вход УВХ равно 0,3 мкс.

$$t_{ah.\kappa} = R_2 \cdot C_2 = 0.3 \cdot 10^{-6}$$

.

Выбираем  $R_2 = 10$  кОм,  $C_2 = 30$  пФ.

Время задержки сигнала на вход АЦП равно 0,8 мкс.

$$t_{y_{BX}} = R_4 \cdot C_4 = 0.8 \cdot$$

мкс.

Выбираем  $R_4 = 10$  кОм,  $C_4 = 80$  пФ.

Время задержки сигнала на вход микропроцессорного устройства равно 170 мкс.

$$t_{AUII} = R_5 \cdot C_5 = 170 \cdot 10^{-6}$$

.

Выбираем R5 = 100 кОм, C5 = 1,7 мкФ.

#### 2.7. Расчёт надёжности вычислительного устройства

При расчёте надёжности принимаются следующие допущения:

- 1. отказы элементов являются независимыми и случайными событиями;

- 2. учитываются только элементы, входящие в задание;

- 3. вероятность безотказной работы подчиняется экспоненциальному закону распределения;

- 4. условия эксплуатации элементов учитываются приблизительно с помощью коэффициентов;

- 5. учитываются катастрофические отказы.

В соответствии с принятыми допущениями в расчётную схему должны входить следующие элементы:

- элемент К1, т. е. количество СИС и БИС;

- элемент К2, т. е. количество ИС малой степени интеграции (МИС);

- элемент КЗ, т. е. количество резисторов;

- элемент К4, т. е. количество конденсаторов:

- элемент К5, т. е. количество светодиодов;

- элемент Кб т. е. количество поеных соединений;

- элемент К7, т. е. количество разъёмов.

В соответствии с расчётной схемой вероятность безотказной работы системы определяется как:

$$P(t) = \prod_{i=1}^{N} P_1(t) \cdot P_2(t) \cdot P_3(t) \cdot \dots,$$

где N – количество таких элементов, используемых в задании;

$P_1$  — вероятность безотказной работы i-ro элемента. Учитывая экспоненциальный закон отказов, имеем:

$$P(t) = \prod_{i=1}^{ni} e^{-\lambda it} - e^{\Sigma} = e^{-\Sigma \cdot \Sigma \lambda it},$$

где ni, — количество элементов одного типа,

$\lambda_j$  – интенсивность отказов элементов j-ro типа. Причём  $\lambda_j = k\lambda \cdot \lambda j_0,$

где kj – коэффициент, учитывающий условия эксплуатации;

$\lambda j_0$  – интенсивность отказов в лабораторных условиях.

Суммарная интенсивность отказов элементов одного типа составит

$$\lambda_{i\Sigma} = \sum_{i=1}^{m} K_{\lambda} \cdot \lambda_{j0} = n_i \cdot k\lambda \cdot \lambda_{j0}.$$

Исходя из условий эксплуатации принимаем  $k\lambda = 1$ . Никаких дополнительных поправочных коэффициентов вводится не будет, так как все элементы системы работают в нормальных условиях, предусмотренных в ТУ на данные элементы.

Для элементов, используемых для построения ВУ, приняты следующие интенсивности отказов:

- Микросхемы с 14 выводами  $\lambda_1 = 4.5 \times 10^{-7}$ ;

- Микросхемы с 16 выводами  $\lambda_2 = 4.0 \times 10^{-7}$ ;

- Микросхемы с 48 выводами  $\lambda 3 = 3.2 \times 10^{-7}$ ;

- Резисторы  $\lambda_4 = 1.0 \times 10^{-5}$ ;

- Конденсаторы электролитические  $\lambda_5 = 0.1 \times 10^{-5}$ ;

- Конденсаторы керамические  $\lambda_6 = 0.04 \times 10^{-5}$ ;

- Светодиоды  $\lambda_7 = 0.26 \times 10^{-5}$ ;

- Паяные соединения  $\lambda_8 = 1.0 \times 10^{-7}$ ;

- Разъёмы с 48 выводами  $\lambda_8 = 0.2 \times 10^{-5}$ .

Исходя из этих значений, можно подсчитать суммарную интенсивность отказов всех элементов одного типа, а затем и для всех элементов ВУ:

$$\begin{split} \lambda_{k1\Sigma} &= N \cdot 4, 5 \cdot 10^{-7} = ...., \\ \lambda_{\hat{\imath} \, \hat{a} \hat{u}} &= \sum_{i=1}^{N} \lambda E_i \; . \end{split}$$

Вероятность безотказной работы ВУ за  $T = 1\ 000$  часов.

$$P(t) = e^{-\lambda_{o \delta u t}},$$

$$P(1000) = e^{-\lambda_{o \delta u t} \cdot 1000}$$

Среднее время наработки на отказ.

# БИБЛИОГРАФИЧЕСКИЙ СПИСОК

- 1. Хилбурн, Дж. Микро-ЭВМ и микропроцессоры / Дж. Хилбурн, П. Джулич. М. : Мир, 1979. 464 с.

- 2. Токхайм, Р. Микропроцессоры: Курс и упражнения / Р. Токхайм. М.: Энергоатомиздат, 1988. 336 с.

- 3. Гилмор, Ч. Введение в микропроцессорную технику / Ч. Гилмор. М. : Мир, 1984.-344 с.

- 4. Вершинин, О. Е. Применение микропроцессоров для автоматизации технологических процессов / О. Е. Вершинин. Л. : Энергоатомиздат, 1986. 208 с.

- 5. Кауфман, М. Практическое руководство по расчётам схем в электронике : справочник / М. Кауфман, Л. Сидман. М. : Энергоатомиздат, 1991. 368 с.

- 6. Ягубов, 3. X. Элементы цифровой техники : учеб. пособие / 3. X. Ягубов. Ухта : УИИ, 1995.-80 с.

- 7. Преснухин, Л. Н. Расчёт элементов цифровых устройств / Л. Н. Преснухин, Н. В. Воробьев, А. А. Шишкевич. М. : Энергоатомиздат, 1991. 526 с.

- 8. Мячев, А. А. Персональные ЭВМ и микро ЭВМ : справочник / А. А. Мячев, В. Н. Степанов. – М. : Радио и связь, 1991. - 320 с.

- 9. Булычёв, А. Л. Аналоговые интегральные схемы : справочник / А. Л. Булычёв. Мн. : Беларусь, 1993. 382 с.

- 10. Шевкопляс, Б. В. Микропроцессорные структуры / Б. В. Шевкопляс. М. : Радио и связь, 1990.-512 с.

# ТЕМЫ ПО КУРСОВОЙ РАБОТЕ

Номер темы выбирается по порядковому номеру в журнале у старосты груп-

пы.

| п/п | Тема                                                                |

|-----|---------------------------------------------------------------------|

| 1   | Автоматизация куста добывающих скважин на основе микропроцессор-    |

|     | ной элементарной базы                                               |

| 2   | Автоматизация куста нагнетательных скважин на основе микропроцес-   |

|     | сорной элементарной базы                                            |

| 3   | Автоматизация дожимной насосной станции на основе микропроцессор-   |

|     | ной элементарной базы                                               |

| 4   | Автоматизация кустовой насосной станции на основе микропроцессор-   |

|     | ной элементарной базы                                               |

| 5   | Автоматизация мультифазной насосной станции на основе микропроцес-  |

|     | сорной элементарной базы                                            |

| 6   | Автоматизация блочной установки подготовки нефти на основе микро-   |

|     | процессорной элементарной базы                                      |

| 7   | Автоматизация блочной установки подготовки газа на основе микропро- |

|     | цессорной элементарной базы                                         |

| 8   | Автоматизация газокомпрессорной станции на основе микропроцессор-   |

|     | ной элементарной базы                                               |

| 9   | Автоматизация газораспределительной станции на основе микропроцес-  |

|     | сорной элементарной базы                                            |

| 10  | Автоматизация газотурбинной электростанции на основе микропроцес-   |

|     | сорной элементарной базы                                            |

| 11  | Автоматизация блока телемеханики газопровода на основе микропроцес- |

|     | сорной элементарной базы                                            |

| 12  | Автоматизация пункта сдачи нефти нефтедобывающей компании на ос-    |

|     | нове микропроцессорной элементарной базы                            |

| 13  | Автоматизация насосной станции поддержания пластового давления на   |

| 4.4 | основе микропроцессорной элементарной базы                          |

| 14  | Автоматизация нефтеперекачивающей насосной станции на основе мик-   |

| 1.5 | ропроцессорной элементарной базы                                    |

| 15  | Автоматизация резервуарного парка нефти на основе микропроцессор-   |

| 1.0 | ной элементарной базы                                               |

| 16  | Автоматизация сливо-наливной эстакады нефтепродуктов на основе      |

| 17  | микропроцессорной элементарной базы                                 |

| 17  | Автоматизация станции пожаротушения на основе микропроцессорной     |

| 10  | элементарной базы                                                   |

| 18  | Автоматизация штангового глубинного насоса на основе микропроцес-   |

| 10  | сорной элементарной базы                                            |

| 19  | Автоматизация системы нефтегазоводоразделителя на основе микропро-  |

| 20  | цессорной элементарной базы                                         |

| 20  | Автоматизация печи прямого нагрева нефти на основе микропроцессор-  |

|    | ной элементарной базы                                             |

|----|-------------------------------------------------------------------|

| 21 | Автоматизация путевого подогревателя нефти на основе микропроцес- |

|    | сорной элементарной базы                                          |

| 22 | Автоматизация установки дозирования реагентов на основе микропро- |

|    | цессорной элементарной базы                                       |

| 23 | Автоматизация блочной котельной на основе микропроцессорной эле-  |

|    | ментарной базы                                                    |

| 24 | Автоматизация блока телемеханики нефтепровода на основе микропро- |

|    | цессорной элементарной базы                                       |

| 25 | Автоматизация блока телемеханики станцией электрохимзащиты трубо- |

|    | провода на основе микропроцессорной элементарной базы             |

| 26 | Автоматизация факельной установки открытого типа на основе микро- |

|    | процессорной элементарной базы                                    |

| 27 | Автоматизация блочного электродегидратора нефти на основе микро-  |

|    | процессорной элементарной базы                                    |

|    |                                                                   |